# MINIMIZING POWER AMPLIFIER MEMORY EFFECTS

#### **ALLEN KATZ\* AND MARC FRANCO**

\*The College Of New Jersey

3 Nami Lane, Unit C-9 / Hamilton, NJ 08619 / Tel: 609.584.8424 / Fax: 609.631.0177 www.lintech.com

# Introduction

Memory Effects (ME) are changes in a Power Amplifier's (PA) non-linear characteristics resulting from the past history of the input signal.

Vo = f(Vin, time)

- Standard predistortion linearization depends on a stable non-linear response, and is particularly degraded by memory effects

- Techniques to reduce PA memory effects will be presented

# OUTLINE

• Why minimize memory effects in PA's ?

- Discuss different sources of ME and how to suppress them

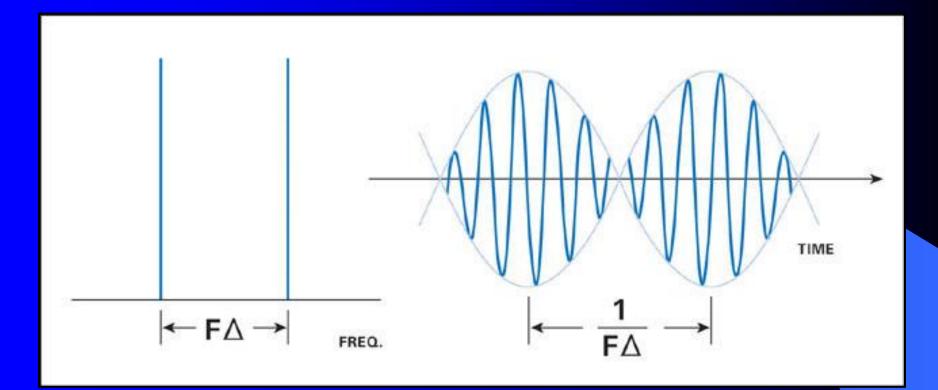

- Frequency ME

- Drain/collector ME

- Gate/base ME

- Device related ME

- Thermal ME

### Summarize and conclude

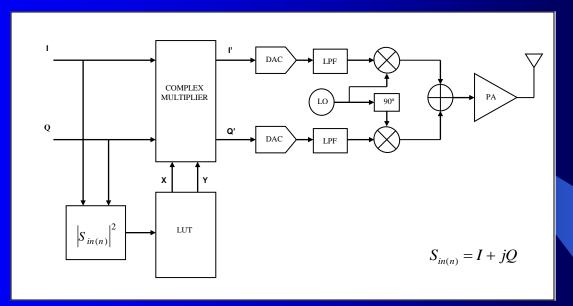

### **BASIC DSP PREDISTORTION (PD) LINEARIZER**

Every input level has a corresponding output level

Correction (mag & phase) in look up tables (LUT) depends on input level

LUT often adaptively updated for slow changes over time

### **BASIC DSP PREDISTORTION LINEARIZER**

- Memory Effects cause correction to depend on recent past

- If correction depends on additional parameters, system can become very complex (huge multi dimensional LUTs, limited processing time and bandwidth)

- Feedback is not a solution because amplifier time delay limits maximum bandwidth

- Best solution is to minimize ME by PA design

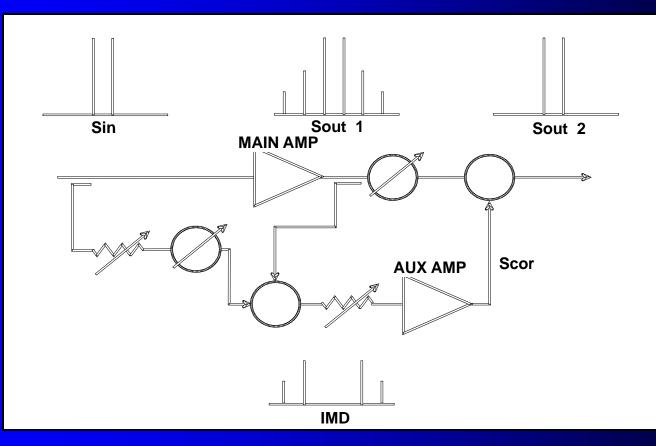

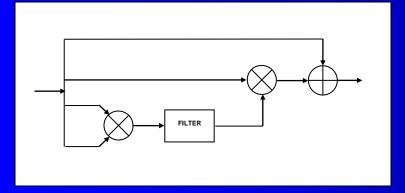

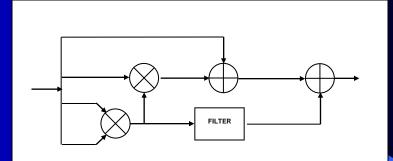

#### **FEEDFORWARD LINEARIZATION**

# Automatically corrects for memory effects, but is more complex and less efficient than predistortion

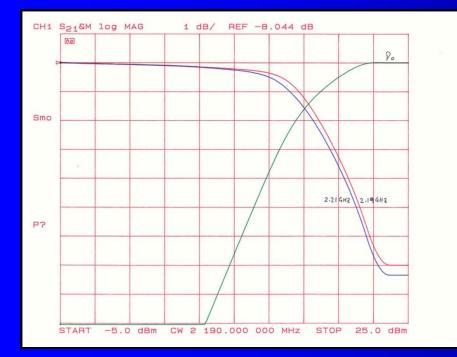

#### GAIN VS. INPUT POWER IS AFFECTED BY FREQUENCY

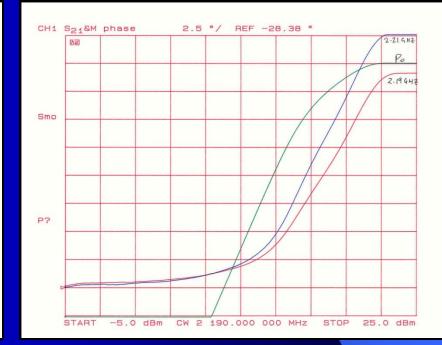

#### PHASE VS. INPUT POWER IS AFFECTED BY FREQUENCY

- Standard predistorter look-up tables have the same correction for every frequency

- Real PA non-linearities do change with frequency

\_\_\_ Linearizer Technology, Inc.™

- No easy circuit solution for wideband signals

- Design PA for as wide a bandwidth as possible

- Avoid frequency selective components

- Achieve low SWR at input and output and maintain it low across full band of interest

- Must equalize small signal gain and phase to achieve good wideband performance

- Adaptive techniques can correct for frequency changes of limited bandwidth signals

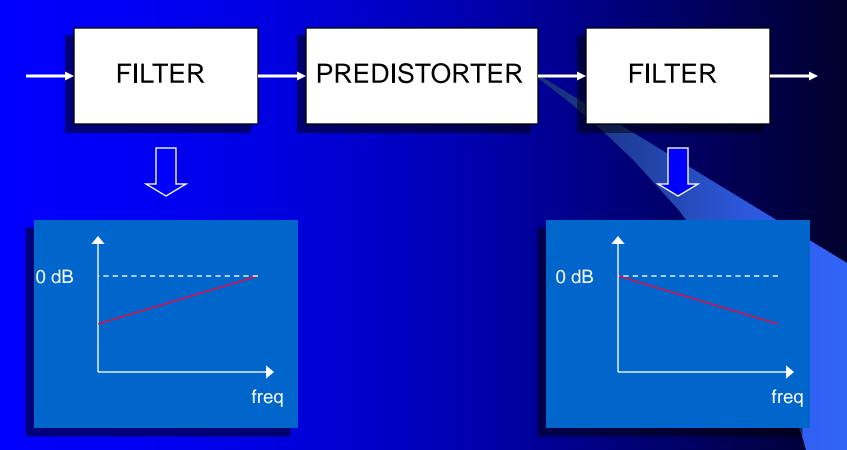

#### Proposed architecture for reducing memory effects produced by frequency sensitivity

Digital linearization across 100 MHz using filters to correct for frequency memory effects

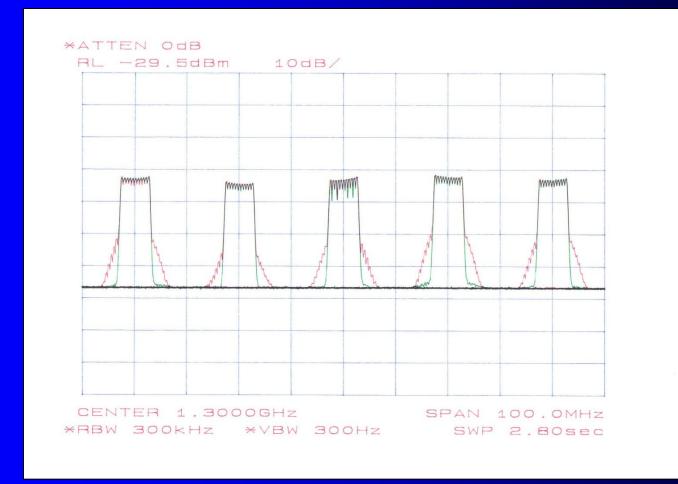

#### Digital linearization across 100 MHz without memory effects correction

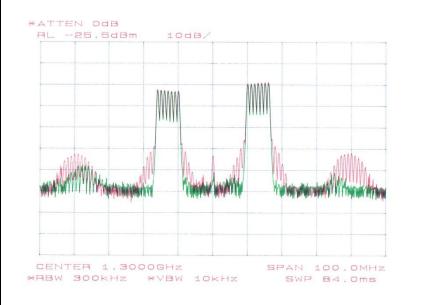

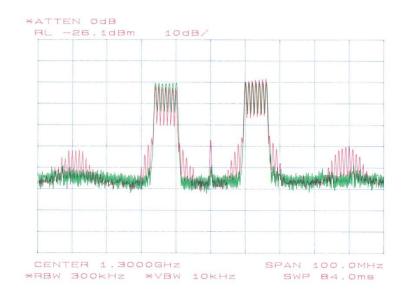

Digital linearization across 100 MHz with memory effects correction

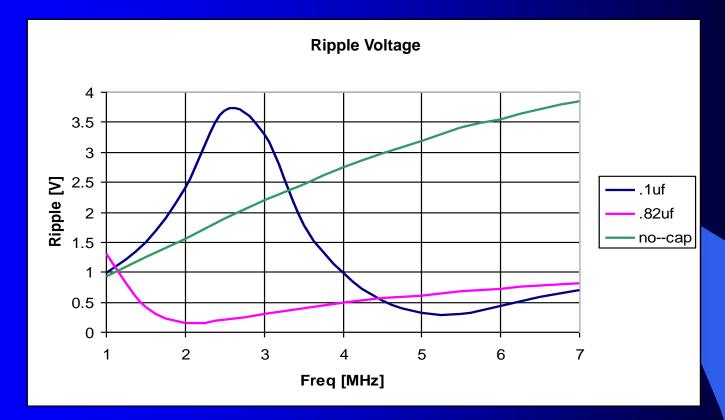

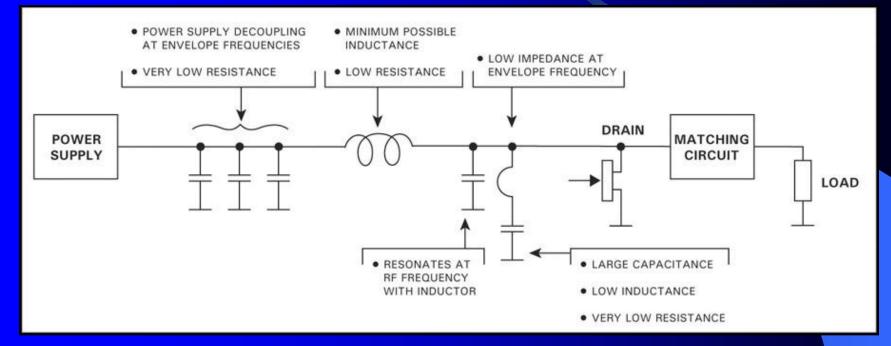

- The major contributor to ME in many PAs is change in drain (or collector) voltage due to non-zero bias/power supply impedance

- All PAs must isolate the RF (i.e. microwave) signal from the dc power supply

- The drain isolation circuit must have a low impedance at the signal's baseband (envelope) frequencies, to avoid envelope dependent voltage changes at the drain

- Even class A PAs will have an envelope dependent voltage change, although the problem becomes worse as a PA's bias moves toward class B

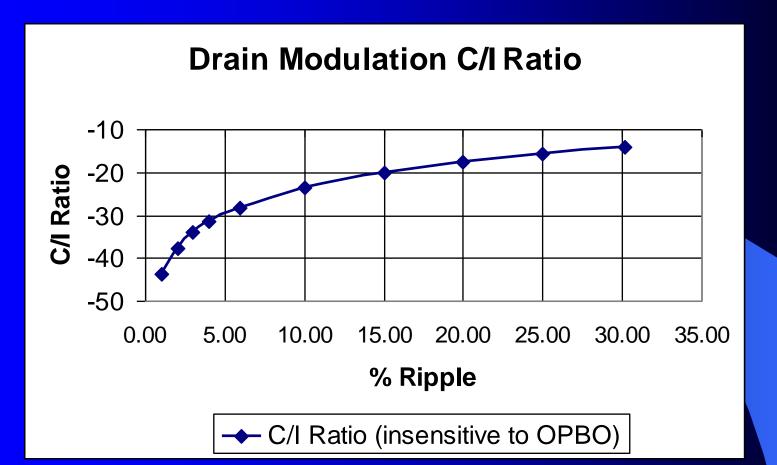

Change in drain voltage amplitude modulates and phase modulates the PA output producing sidebands at the same frequencies as intermodulation distortion (IMD)

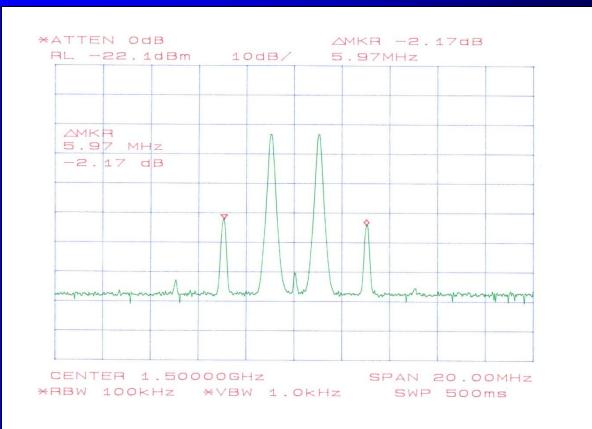

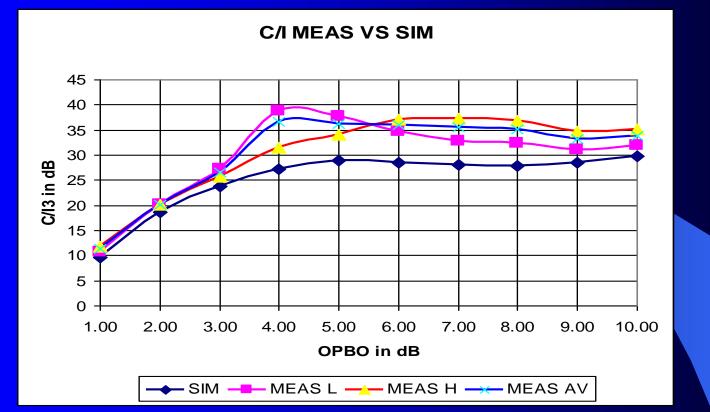

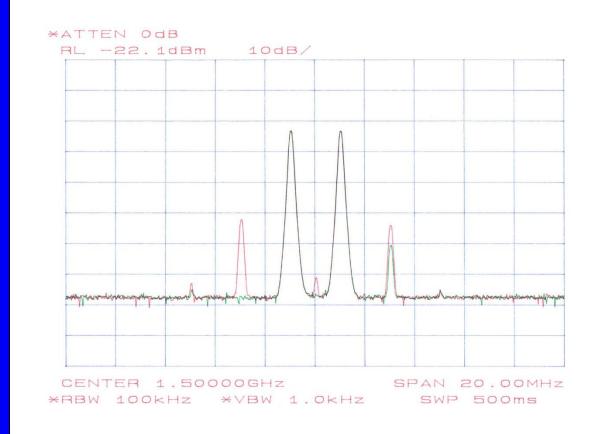

Non-symmetrical IMD products can result from the interaction of device and drain / gate ripple induced IMD (simplest test for PA memory effects)

Overall carrier to interference (C/I) ratio can be higher than expected based on the PA transfer characteristics

This effect is the result of IMD cancellation

Memory effects produce non-even cancellation of IMD

**Compromise IMD cancellation can be achieved, but may not be sufficient**

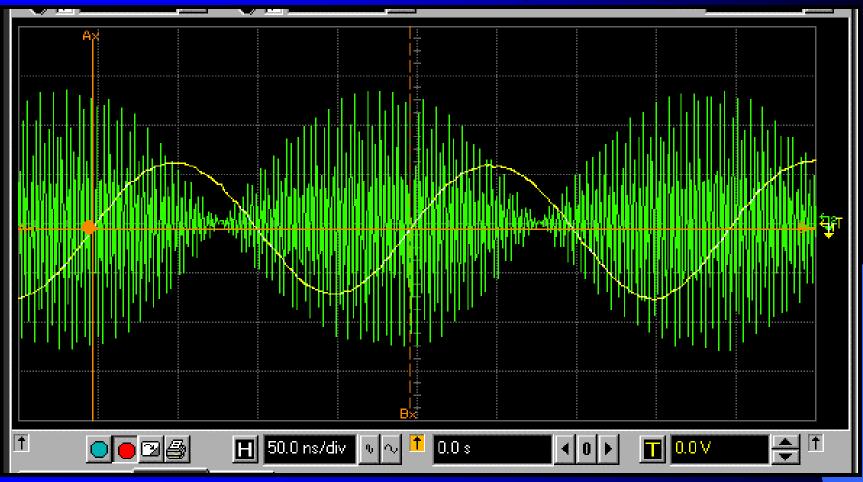

#### RF ENVELOPE (GREEN) IS ~ 140° OUT OF PHASE WITH DRAIN RIPPLE (YELLOW)

IMDs caused by the PA non-linearity subtract from the ripple induced IMDs

\_\_\_\_ Linearizer Technology, Inc.™

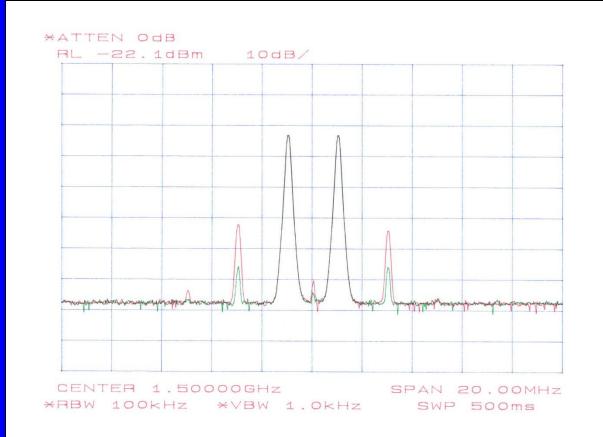

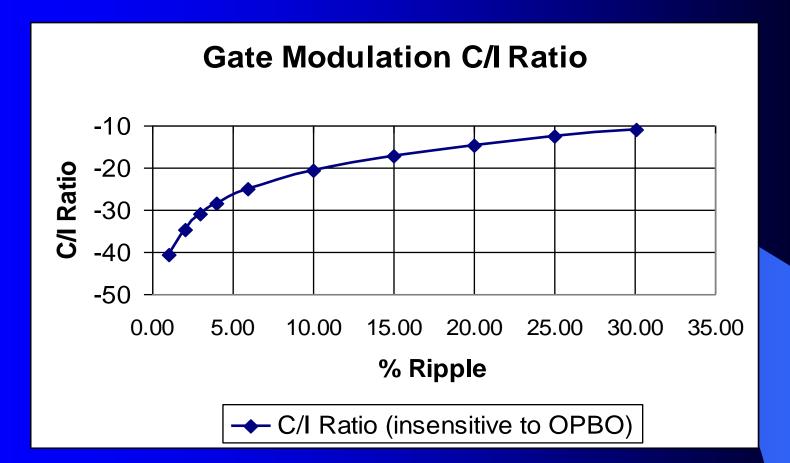

Measurement of the sensitivity of a GaAs FET PA to drain modulation

Ripple < 2% is required for C/I < 40 db

# Amplifier linearity can change and often degrades with increasing carrier spacing

For wide or even moderate bandwidth signals, the drain ripple is not a trivial problem

Consider a 250 MHz PA with a 25 MHz multi carrier signal

# DRAIN/COLLECTOR MEMORY EFFECTS MINIMIZATION

A low impedance network at envelope frequencies across the drain and effective power supply decoupling can minimize memory effects

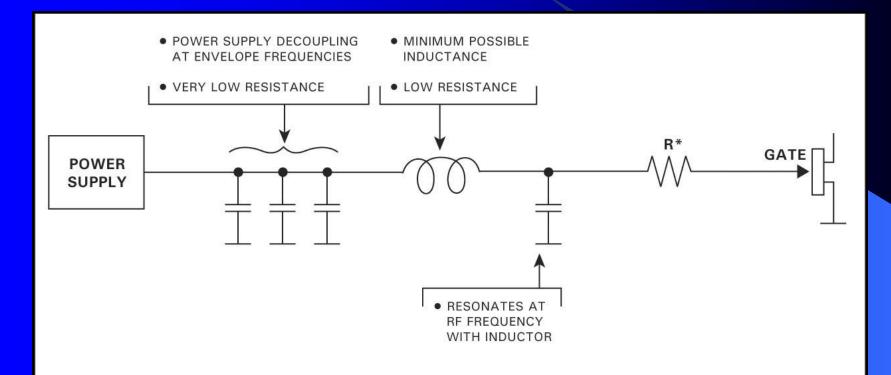

# **GATE/BASE MEMORY EFFECTS**

- Change in gate (or base) voltage can also be a significant contributor to memory effects

- This problem can be more difficult to solve than for the drain / collector case, and is quite different for BJT and FET devices

- PA stability can be a major concern

- Low currents are involved, so good power supply decoupling is easier to achieve

- GaAs FET gate supply must achieve good voltage regulation in spite of current flowing due to RF rectification by the gate-source diode

# **GATE MEMORY EFFECTS MINIMIZATION**

The value of R\* must be carefully chosen to provide a compromise between stability and bias-induced memory effects

# **GATE MEMORY EFFECTS**

Measurement of the sensitivity of a GaAs FET PA to gate modulation

Ripple < 1% is required for C/I < 40 db

\_\_\_ Linearizer Technology, Inc.™

# THERMAL MEMORY EFFECTS

- Major source of thermal memory effects is device junction temperature changes as a function of envelope frequency, particularly below 100 KHz

- Choice of device can minimize temperature memory effects. Temperature affects some devices less

- Bias class can also minimize temperature effects. Class A is less affected than class B, but has low efficiency

- Long term temperature changes (that do not depend on the envelope frequency) can also be considered a memory effect. Good thermal design or an adaptive circuitry can minimize this problem

# **DEVICE RELATED MEMORY EFFECTS**

- Some devices display changes in non-linear characteristics with envelope frequency that cannot be explained by bias modulation

- This phenomena appears related to current flow and charge trap build up. Some sources have attributed it to very small time-constant thermal effects

- Different devices show varying sensitivity. HBT, some LDMOS and GaN devices appear particularly sensitive

- No recommended solution except careful device selection

# ADDITIONAL MEMORY EFFECTS CANCELLATION METHODS

**Envelope Filtering**

**Envelope** Injection

#### These methods are covered in the book "Distortion in RF Power Amplifiers" by J. Vuolevi and T. Rahkonen

It is difficult to eliminate distortion caused by MEs using linearization

Bias voltage variations (both drain/collector and gate/base) are a major cause of MEs

Thermal change is another important source of MEs

MEs can be minimized by careful electrical and mechanical design

# Where to Get More Information

Vuolevi and Rahkonen, "Distortion in RF Power Amplifiers", Artech House, 2003.

Cripps, "RF Power Amplifiers for Wireless Communications", Artech House, 1999.

Cripps, "Advanced Techniques in RF Power Amplifier Design", Artech House, 2002.

W. Bosch, G. Gatti, "Measurement and Simulation of Memory Effects in Predistortion Linearizers", IEEE Transactions on Microwave Theory and Techniques, Vol. 37, No. 12, December1989.

A. Katz, "Linearization: Reducing Distortion in Power Amplifiers", IEEE Microwave Magazine, December 2001.

S. Boumaiza, F. Ghannouchi, "Thermal Memory Effects Modeling and Compensation in RF Power Amplifiers and Predistortion Linearizers", IEEE MTT, December 2003.

K. Cho, J. Choi, J. Kim, B. Lee, N. Kim, J. Lee, S. Stapleton, "An Analog Compensation Method for Asymmetric IMD Characteristics of a Power Amplifier", 2003 IEEE MTT-S Digest.

H. Ku, J. Kenney, "Behavioral Modeling of RF Power Amplifiers Considering IMD and Spectral Regrowth Asymmetries", 2003 IEE MTT-S.

N. Borges de Carvalho, J. Pedro, "A Comprehensive Explanation of Distortion Sideband Asymmetries", IEEE MTT, September 2002.